#### FIPS 140-2 Level 3

#### Security Policy of Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f

August 2015

Version 2.3

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f

Version 2.3

**Title:** Security Policy of Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR),v1.0f **Contributing Authors**: Roland Atoui, Clifford Wayne

Oracle Corporation World Headquarters 500 Oracle Parkway Redwood Shores, CA 94065 U.S.A. Worldwide Inquiries: Phone: +1.650.506.7000 Fax: +1.650.506.7200 oracle.com

Oracle is committed to developing practices and products that help protect the environment

Copyright © 2014, Oracle and/or its affiliates. All rights reserved. This document is provided for information purposes only and the contents hereof are subject to change without notice. This document is not warranted to be error-free, nor subject to any other warranties or conditions, whether expressed orally or implied in law, including implied warranties and conditions of merchantability or fitness for a particular purpose. We specifically disclaim any liability with respect to this document and no contractual obligations are formed either directly or indirectly by this document.

CIPURSE is a registered trademark of the OSPT - Open Standard for Public Transportation Alliance e.V.

Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners.

#### Hardware and Software, Engineered to Work Together

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f

Copyright © 2014, Oracle and/or its affiliates. All rights reserved This document may be freely reproduced and distributed whole and intact, including this copyright notice.

### Contents

| Contents                                    | 1  |

|---------------------------------------------|----|

| 1 Introduction                              | 5  |

| 1.1 Context                                 | 5  |

| 1.1 Distribution Policy                     |    |

| 1.2 Document Structure                      |    |

| 2 Cryptographic Module Overview             | 7  |

| 2.1 CM Description                          | 7  |

| 2.1.1 CM Purpose                            |    |

| 2.1.2 Core Functionalities                  | 9  |

| 2.1.2.1 Applet Downloading                  | 9  |

| 2.1.2.2 Card Management                     | 9  |

| 2.1.2.3 Services to Applets                 |    |

| 2.1.3 Security Level                        | 10 |

| 3 Cryptographic Module Specification        | 11 |

| 3.1 CM Architecture                         |    |

| 3.1.1 IC Hardware and Firmware              | 12 |

| 3.1.2 Java Card Platform                    | 13 |

| 3.2 Cryptographic Boundary                  | 14 |

| 3.3 CM Cryptographic Functions              |    |

| 3.3.1 Cryptographic Keys                    | 15 |

| 3.3.2 Public Keys                           | 17 |

| 3.3.3 PIN                                   | 17 |

| 3.3.4 Audit events and data                 | 17 |

| 3.4 FIPS 140-2 Approved Modes of Operation  |    |

| 3.4.1 Versions and Mode of Operation        |    |

| 3.4.2 CM Identification                     | 19 |

| 4 Cryptographic Module Ports and Interfaces | 21 |

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

| 4.1 Communication Interfaces                                                                        | 21 |

|-----------------------------------------------------------------------------------------------------|----|

| 4.1.1 Logical Interfaces                                                                            | 21 |

| 4.1.2 Physical Interfaces                                                                           | 22 |

| 4.2 Packages                                                                                        | 25 |

| 5 Roles, Services and Authentication                                                                | 27 |

|                                                                                                     |    |

|                                                                                                     |    |

| 5.2 Services                                                                                        |    |

| 5.2.1 Card Management Services Available to off Card Entities<br>5.2.1.1 Non Authenticated Services |    |

| 5.2.1.2 Services Requiring Authentication and Manipulating CSPs                                     |    |

| 5.2.2 Cryptographic Services Available via Java Card API                                            |    |

| 5.2.2.1 FIPS 140-2 Approved Algorithms                                                              |    |

|                                                                                                     |    |

| 6 Security Requirements                                                                             |    |

| 6.1 Identification and Authentication of Roles                                                      |    |

| 6.1.1 Identification                                                                                |    |

| 6.1.2 Authentication                                                                                | 33 |

| 6.2 Integrity and Confidentiality of Loaded Application Code                                        |    |

| 6.3 Authentication of Loaded Application Code                                                       | 34 |

| 6.3.1 DAP Verification                                                                              | 34 |

| 6.4 CSP Secure Management                                                                           | 35 |

| 6.4.1 Cryptographic Key and PIN Entry                                                               | 35 |

| 6.4.2 Cryptographic Keys and User PIN Contents Zeroization                                          | 35 |

| 6.4.3 Key Generation                                                                                |    |

| 6.4.4 Key Loading                                                                                   |    |

| 6.4.5 Key Storage                                                                                   |    |

| 6.4.6 Key Establishment                                                                             |    |

| 6.4.7 Key Distribution                                                                              |    |

| 7 Physical Security                                                                                 |    |

| 7.1 Physical Security Mechanisms                                                                    |    |

| 9 Mitigation of Other Attacks                                                                       | 20 |

| 8 Mitigation of Other Attacks                                                                       |    |

| 8.1 Power and Electromagnetic Analysis Attacks                                                      |    |

| 8.1.1 Countermeasures                                                                               |    |

| 8.2 Timing Analysis Attacks                                                                         |    |

| 8.2.1 Countermeasures                                                                               |    |

| 8.3 Fault Induction Attacks                                                                         |    |

|                                                                                                     |    |

| 8    | 8.3.1 Countermeasures                                          |    |

|------|----------------------------------------------------------------|----|

| 9 S  | Self-Tests                                                     | 41 |

| 9.1  | 1 Power Up Self -Tests                                         |    |

| 9    | 9.1.1 Deterministic Random Number Generator Test               | 41 |

| 9    | 9.1.2 Cryptographic Algorithm Known Answer Tests               |    |

| 9    | 9.1.3 Software/Firmware Integrity KAT                          |    |

| 9    | 9.1.4 Critical Functions Tests                                 | 42 |

| 9.2  | 2 Conditional Self-Tests                                       |    |

| 9    | 9.2.1 Pair-wise Consistency Test (for public and private keys) |    |

| 9    | 9.2.2 Firmware Load Test.                                      | 42 |

| 9    | 9.2.3 Key Entry Tests                                          | 43 |

| 9    | 9.2.4 Continuous RNG Testing                                   | 43 |

| 9    | 9.2.5 Bypass Testing                                           | 43 |

| 10   | Security Policy - Check List Tables                            | 44 |

| 10.1 | .1 Roles and Required Identification and Authentication        |    |

| 10.2 | .2 Strength of Authentication Mechanisms                       |    |

| 10.3 | .3 Services Authorized for Roles                               |    |

| 10.4 | .4 Access Rights Within Services                               |    |

| 10.5 | .5 Physical Security Requirements                              |    |

| 10.6 | .6 Mitigation of Other Attacks                                 |    |

| A    | References                                                     | 49 |

| B    | Acronyms                                                       |    |

#### List of Tables

| Table 1: Security Level                                                                  | 10           |

|------------------------------------------------------------------------------------------|--------------|

| Table 2: Cryptographic Algorithms                                                        | 15           |

| Table 3: Critical Security Parameters - Secret Symmetric Keys                            | 16           |

| Table 4: Critical Security Parameters - Public Assymetric Keys                           | 17           |

| Table 5: Critical Security Parameters - Global PIN                                       | 17           |

| Table 6: Critical Security Parameters - Counters                                         | 17           |

| Table 7: Product and Package Combination                                                 |              |

| Table 8: Versions and Mode of Operations Indicators                                      | 19           |

| Table 9: Tag 'DF10'                                                                      | 20           |

| Table 10: Tag 'DF11'                                                                     | 20           |

| Table 11: Logical Interface                                                              | 21           |

| Table 12: CM ISO 7816 Interface Contact Assignments                                      | 23           |

| Table 13: IC Pad Descriptions and Logical Interface Types                                | 24           |

| Table 14: Logical Interfaces With Physical Interface Connections                         | 25           |

| Table 15: Supported Packages                                                             |              |

| Table 16: Roles                                                                          |              |

| Table 17: Unauthenticated Services                                                       | 29           |

| Table 18: Card Content Manager Services and their CSP Usage                              |              |

| Table 19: Cryptographic Services and Authentication services available to applet through | the standard |

| Java Card API                                                                            |              |

| Table 20: FIPS Approved Cryptographic Algorithms                                         | 32           |

| Table 21: Roles and Required Identification and Authentication - Check-List              | 44           |

| Table 22: Strength of Authentication Mechanisms - Check-List                             | 44           |

| Table 23: Services Authorized for Roles - Check-List                                     |              |

| Table 24: Access Rights Within Services - Check-List                                     |              |

| Table 25: Physical Security Requirements - Check-List                                    |              |

| Table 26: Mitigation of Other Attacks - Check-List                                       |              |

#### Table of Figures

| Figure 1. CM Architecture Overview                                       | 11 |

|--------------------------------------------------------------------------|----|

| Figure 2. Cryptographic Boundary – Hardware Architecture                 | 12 |

| Figure 3. Relationship of CM Software Module and Supporting Applications | 13 |

| Figure 4. Cryptographic Module Boundary                                  | 14 |

| Figure 5: ISO 7816 Interface Contact Pad Designations and Locations      | 23 |

| Figure 6: IC Die Pad Designations and Locations                          | 24 |

#### CHAPTER

### Introduction

his document describes how the Cryptographic Module (CM) meets all the requirements for level 3 validation criteria specified in [FIPS PUB 140-2]. The CM is a Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR).

This Security Policy is intended to specify the security rules under which the CM operates and does not describe the security requirements for the entire product.

#### 1.1 Context

This is a non-proprietary Cryptographic Module Security Policy for the Cryptographic Module (CM) which consists of the Infineon Technologies Dual Interface Security Controller M7892 with RSA, EC and SHA cryptographic libraries and the Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) binary code.

The Dual Interface Security Controller M7892 is a member of the Infineon Technologies AG high security controller family SLE70 meeting the highest requirements in terms of performance and security. The SLE70 family provides a common architecture upon which specific products can be tailored for different usages such as high security and contactless applications which can be identified by SLE78 which is the family of the IC that we are targeting in this evaluation.

This Security Policy describes how the Dual Interface Security Controller SLE78 and Java Card Platform binary code meets the security requirements of FIPS 140-2 and CM's operation in a secure FIPS 140-2 mode. This policy was prepared as part of the Level 3 FIPS 140-2 validation of the module. FIPS 140-2 (Federal Information Processing Standards Publication 140-2 — *Security Requirements for Cryptographic Modules*) details the U.S. Government requirements for cryptographic modules. More information about the FIPS 140-2 standard and validation program is available on the National Institute of Standards and Technology (NIST) Cryptographic Module Validation Program (CMVP) website at <a href="http://csrc.nist.gov/cryptval/">http://csrc.nist.gov/cryptval/</a>.

The Dual Interface Security Controller SLE78 with the Java Card Platform implementation binary code is referred to in this document as CM, Cryptographic Library, Software Library, Cryptographic module, software module, or module.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

#### 1.1 Distribution Policy

With the exception of this Non-Proprietary Security Policy, the FIPS 140-2 Validation Documentation is proprietary to Oracle Corporation and is releasable only under appropriate non disclosure agreements. For access to these documents, please contact Oracle Corporation.

#### 1.2 Document Structure

This document is structured as follows:

- Chapter 2 describes the Cryptographic Module (CM), defines its main purpose, and identifies its security levels.

- Chapter 3 describes the CM architecture, boundary, functions, CSPs and modes of operation.

- Chapter 4 describes the ports and interfaces (physical and logical) and the information passing over them.

- · Chapter 5 describes the roles, services and authentication provided by the CM.

- Chapter 6 describes the security policy for the enforcement of identity based authentication and data, cryptographic key and code integrity and confidentiality.

- Chapter 7 describes physical security mechanisms provided by the CM.

- Chapter 8 describes how the cryptographic module provides protection for the CSPs against noninvasive attacks and the effectiveness of the mitigation techniques.

- Chapter 9 describes self-tests ensuring that the CM is functioning properly.

- · Chapter 10 summarizes the security policy check list tables.

CHAPTER

## 2 Cryptographic Module Overview

his chapter provides a global description of the Cryptographic Module (CM), defines its main purpose and security level.

#### 2.1 CM Description

The CM is a Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) mounted in a smart card form factor.

- CM name/version: Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f

- · CM Hardware ID: M7892B11 (Smart Card IC)

- CM Platform Commercial ID's: SLE78CLFX400VP(M), SLE 78CLFX408AP(M)

- CM Interface Package ID's:

- P-MCS8-2-1 (ISO/IEC 14443)

- P-MCC8-2-6 (ISO/IEC 14443)

- o S-MFC6.8-8-1 (ISO/IEC 7816-3)

- S-COM8.6-6-1 (ISO/IEC 7816-3 and 14443)

- o P-M8.4-8-3 (ISO/IEC 7816-3 and 14443)

- o S-MID4.8-8-1 (ISO/IEC 7816-3)

- o S-COM10.6-6-1 (ISO/IEC 7816-3 and 14443)

- o PG-USON10-1 (ISO/IEC 7816-3)

The CM name/id consists of the following placeholder:

- the first x is for the available interface (can be 'C', 'L', or 'D' for the Contact based, contact Less or Dual Interface)

- the second x is for the available cryptography (can be 'A' for symmetric and asymmetric cryptography, and 'B' for only symmetric cryptography)

- The number yyy the available user memory (it is '160' for 160 kB)

- the last letter z represents the product (can be 'A' for ePassport, 'B' for eDriving License, 'C' for National eID Open Platform, or 'D' for National eID with applications)

The CM is a single-chip cryptographic module mounted in a smart card and sets a new, improved standard of integrated security features, thereby meeting the requirements of all smart card and other related applications or form factors, such as information integrity, access control, mobile telephone and identification, as well as uses in electronic funds transfer and healthcare systems.

The Java Card Platform is secure execution environment consisting of a Java Card Runtime, Java Card Virtual Machine, Java Card API and Global Platform Card Manager along with native cryptographic library calls made available to applets through Java Card APIs. The CM is compliant with Java Card specifications version 3.0.1 Classic Edition ([JCVM3], [JCRE3], [JCAPI3]) and the Global Platform card specification version 2.2 [GP]. In particular, it implements the GlobalPlatform ID Configuration 1.0 [GP\_ID]. The cryptographic services offered by the CM are provided to the applets through the Java Card API.

The Infineon Technologies Dual Interface Security SLE78 consists of integrated circuits manufactured by Infineon Technologies AG in a 90 nm CMOS-technology (L90) and provides real 16-bit CPUarchitecture that is compatible with Intel 80251 architecture. The SLE78 dual interface controller meets the highest requirements in terms of performance and security and provides maximum flexibility in using the communication protocols such as ISO 7816, ISO 14443 Type A and Type B. The Security Controller M7892 can communicate using either the contact based or the contactless interface, enabling user implementation of contact based or contactless communication.

The SLE78 is used in smart cards for security-relevant applications. It has also been used as a development platform for smart card operating systems in accordance with the lifecycle model from [1]. The term Smartcard Embedded Software is used in this document to refer to all operating systems and applications stored and executed on the IC regardless whether it is a smartcard or another application of form factor.

The following is a list of features provided by the SLE78 Smart Card IC:

- · 24-bit linear addressing

- Up to 16 MByte of addressable memory

- Register-based architecture (registers can be accessed as bytes, words (2 bytes), and double words (4 bytes))

- 2-stage instruction pipeline

- Extensive set of powerful instructions, including 16-bit and 32-bit arithmetic and logic instructions

- CACHE with single-cycle access searching

- · 16-bit ALU

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

#### 2.1.1 CM Purpose

The main purpose of the CM is to provide cryptographic services to applets through the Java Card API to perform on-device cryptographic operations in a FIPS 140-2 compliant runtime environment where highly secure applications are in use and of course in any other application as well. This CM is intended for use by governmental, corporate, transport and payment markets, or wherever a secure root of trust is required. Various types of applications can use this CM, for example in closed loop logical access controls, physical access controls, secure internet access control and internet authentication, or as multi-application token or simply as encrypted storage.

Operating system(s) the module was tested on: Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR), v1.0f

Data integrity and security are provided through the cryptographic services and defensive characteristics of the CM implementation. The CM supports standard AES, TDES, DSA, RSA, ECDSA, and SHA cryptographic algorithms. Both CM firmware and hardware provide module security. In addition, the CM hardware provides tamper-resistance and tamper-evidence features that meet FIPS 140-2 Level 3 physical security requirements. However, FIPS 140-2 validation does not include privileged applications.

#### 2.1.2 Core Functionalities

The main functionalities provided by the CM are applet downloading, card management, and specific security Java Card API services provided to the applets.

#### 2.1.2.1 Applet Downloading

The Card Manager is a privileged applet defined in the GlobalPlatform specification that enables secure downloading of applications. The card manager implements the policies and security aspects of the card issuer and contains the keys needed to download an applet or a package to the smart card. In accordance with [JCRE3], the installer is the CM component that loads, links, and installs new packages. Once selected, the installer receives the CAP file, stores the classes of the package on the card, initializes any static data, and installs any applets contained in the package.

#### 2.1.2.2 Card Management

In accordance with the Global Platform Card Specification 2.2 [GP], the card manager supports a multi-application runtime environment and provides the Global Platform framework facilities required for secure loading and interoperability of different applications. The card manager is responsible for the administration of the smart card and is conformant to the Global Platform Card Specification 2.2 [GP]. In accordance with [JCRE3] and [GP], the card manager provides administration of the smart card by:

- Managing the life cycle of the installed applications (applets) and the card.

- Managing the security domains and enforcing card issuer security policies.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

• Ensuring secure communication between the application instances on the card and the card administrator.

The Card can be set to run in GP mode or GP ID mode. If the card is configured for GP mode, SSDs follow the GlobalPlatform Card Specification v2.2 requirements [GP]. If the card is configured for GP ID mode, SSDs behave in accordance with the GlobalPlatform ID Configuration specification [GP\_ID]. When GP\_ID mode is enabled, the ISD is required to use SCP 03 option 0x10.

Optionally, the TOE can be configured to behave like a static Java Card Platform where loading of applets is disabled.

#### 2.1.2.3 Services to Applets

The Java Card Platform provides the applets with a set of security services in order to enforce a certain security level for applets execution. These security services are available to the applets through the Java Card API.

#### 2.1.3 Security Level

| Security Requirement                         | Level |

|----------------------------------------------|-------|

| 1. Cryptographic Module Specification        | 3     |

| 2. Cryptographic Module Ports and Interfaces | 3     |

| 3. Roles, Services, and Authentication       | 3     |

| 4. Finite State Model                        | 3     |

| 5. Physical Security                         | 3     |

| 6. Operational Environment                   | n/a   |

| 7. Cryptographic Key Management              | 3     |

| 8. EMI/EMC                                   | 3     |

| 9. Self-Tests                                | 3     |

| 10. Design Assurance                         | 3     |

| 11. Mitigation of Other Attacks              | 3     |

Table 1: Security Level

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

CHAPTER

# **3** Cryptographic Module Specification

This chapter describes the Cryptographic Module architecture, its boundary, functions, and modes of operation.

#### 3.1 CM Architecture

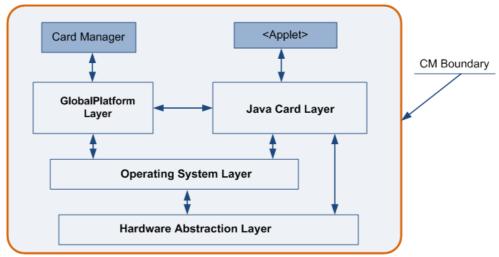

The CM architecture consists of several abstraction layers build on the SLE78 Smart Card and acting in concert to create an environment that provides data integrity and security for the downloading and execution of applets. Figure 1 provides an overall view of the CM architecture.

Figure 1. CM Architecture Overview

The GlobalPlatform (GP) services rely on both the Java Card platform and the operating system services. This component implements the GlobalPlatform card specification, version 2.2, which

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

defines the infrastructure for development, deployment and management of smart cards. The GP supports Security domains and secure channel protocols.

- Java Card services rely on the operating system and the HAL services. It complies with the specifications for the Java Card Platform, Version 3.0.1, Classic Edition. These services include the security inherent in the Java Card programming language.

- The Operating System services rely on the Hardware Abstraction Layer. It provides a memory manager, cryptography engine and input/output.

- The Hardware Abstraction Layer (HAL) interacts directly with the hardware represented in Section 3.1.1. The HAL implements CPU control, card initialization, memory operations, interruption control, and support for cryptography on the chip.

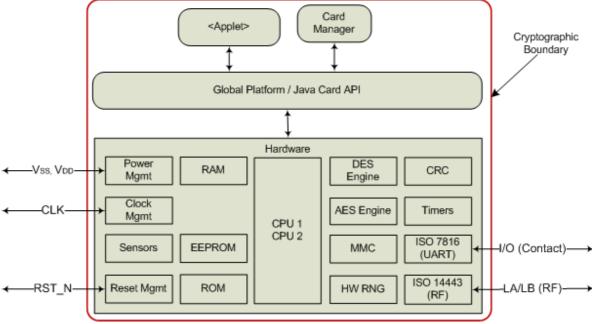

#### 3.1.1 IC Hardware and Firmware

The IC portion of the CM contains specific IC dedicated firmware along with RSA, EC and SHA cryptographic libraries. Figure 2 provides a view of the hardware architecture of the CM.

Figure 2. Cryptographic Boundary – Hardware Architecture

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

#### 3.1.2 Java Card Platform

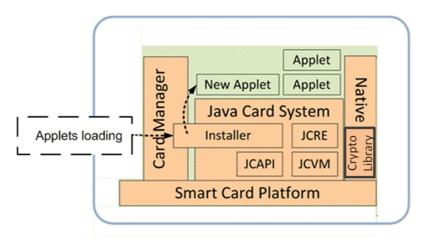

Figure 3 describes the relationship of the Cryptographic Module (CM) software module and supporting applications.

Figure 3. Relationship of CM Software Module and Supporting Applications

The Java Card Platform includes the Java Card RE (JCRE), Java Card VM (JCVM), Java Card API (JCAPI), Card Manager, and Global Platform. The Java Card System along with additional native code is embedded in a Java Card Platform (JCP) as part of the CM and is compliant with Java Card specifications versions 3 Classic Edition, including post-issuance downloading of applications verified off-card.

Components of JCP can be grouped into core and optional components. Core components implement core functionality of the JCP and are required for all possible configurations. The core component group consists of modules from the Java Card Platform, version 3.0.1 and Global Platform 2.2. The operating system and native primitives are tightly integrated with the Infineon libraries and hardware to provide maximum security and performance. Optional components implement optional functionality and are included in configurations only as their functionality is required. Components of the JCP include the following:

- JCAPI The application programming interface for Java Card.

- JCVM The Java Card virtual machine is a subset of the Java virtual machine, and is designed to be run on smart cards and other resource-constrained devices. The Java Card virtual machine acts as an engine that loads Java class files and executes them with a particular set of semantics.

- · JCRE A framework for running Java programs on the card.

- Extended Crypto Cryptographic capabilities have been extended in several ways. Oracle has added additional algorithms and key type support beyond that called out in the Java Card 3.0.1

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

specifications. In addition, some proprietary Infineon cryptographic acceleration classes have been integrated in the JCP.

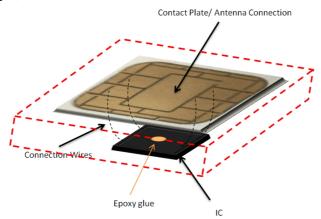

#### 3.2 Cryptographic Boundary

Figure 4 bellow illustrates (in a red-dashed box) the cryptographic boundary of one IC package example. The cryptographic boundary includes the outer perimeter of the IC package (This is valid for all the supported packages).

Figure 4. Cryptographic Module Boundary

#### 3.3 CM Cryptographic Functions

The module provides cryptographic services to end-user applications. Only those cryptographic algorithms marked as "Available in FIPS mode" in Table 2 s are made available to applets through the Java Card APIs. Once the module has entered a FIPS-approved mode of operation, all access to non-approved algorithms is denied to the Java Card applets at runtime except for the key establishment function. Note that in our CM, only the ISD is considered as a runtime instantiated applet, therefore, security services not used by the ISD are not available to any of the current users of the module.

Table 2 describes the cryptographic algorithms, modes, and keys provided by the CM.

| Algorithm                  | Reference   | Modes   | Keys Lengths            | Available in<br>FIPS Mode |

|----------------------------|-------------|---------|-------------------------|---------------------------|

| Symmetric Key – Encryption |             |         |                         |                           |

| AES                        | [2] and [3] | ECB,CBC | 128 bit,192 bit,256 bit | YES                       |

| TDES                       | [4]         | ECB,CBC | 168 bit                 | YES                       |

| Asymmetric Key – Signature | 1           | 1       | L                       | I                         |

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

| Algorithm                               | Reference        | Modes       | Keys Lengths            | Available in<br>FIPS Mode |

|-----------------------------------------|------------------|-------------|-------------------------|---------------------------|

| DSA                                     | [5]              | N/A         | L=2048, N=256           | YES                       |

| RSA                                     | [6] and [7]      | N/A         | 2048 bit (CRT)          | YES                       |

| ECDSA                                   | [5]              | N/A         | 224 bit- 521 bit        | YES                       |

| Hashing                                 |                  |             |                         |                           |

| SHA-1 <sup>1</sup>                      | [8]              | N/A         | 160 bit                 | YES                       |

| SHA-224, SHA-256, SHA-384,<br>SHA-512   | [8]              | N/A         | 224-512 bit             | YES                       |

| Random Number Generators                |                  | N/A         | AES-128 bit             | YES                       |

| CTR_DRBG (AES-128)                      | [12]             | -           |                         | _                         |

| Nondeterministic TRNG<br>(Seeding Only) | [17] Class<br>P2 | N/A         | N/A                     | YES                       |

| Message Authentication                  | [12]             |             | 168 bit                 | YES                       |

| T DES IMAC                              | [13]             | CBC-<br>MAC | 168 DIT                 | YES                       |

| AES CMAC                                | [14]             | CMAC        | 128 bit,192 bit,256 bit | YES                       |

| Key Establishment                       |                  |             |                         |                           |

| ECDH <sup>2</sup>                       | [18]             | N/A         | 224 bit - 521 bit       | YES <sup>3</sup>          |

Table 2: Cryptographic Algorithms

#### 3.3.1 Cryptographic Keys

The following cryptographic keys are critical to security as the mechanisms for authentication, data integrity and confidentiality heavily rely on them. All cryptographic keys are stored in plaintext relying on hardware countermeasures for its integrity protection. The CO and Dev keysets are used for administrative purposes, i.e. card content management and key loading and are the root keys in the creation of session keys used to establish a secure channel. All keys including CO and Dev keysets can be loaded or replaced with the GP's PUT\_KEY APDU command. Such key handling is secured by the Security Domain's symmetric crypto algorithm (128-bit AES).

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

<sup>&</sup>lt;sup>1</sup> SHA-1 is used during RSA signature verification only.

<sup>&</sup>lt;sup>2</sup> EC Diffie-Hellman key establishment methodology provides between 112 and 256 bits of encryption strength.

<sup>&</sup>lt;sup>3</sup> This algorithm is non-FIPS approved but allowed cryptographic function.

Additional details regarding each cryptographic key and CSP are provided in the following tables.

| Кеу      | Description and Usage                                                                                                                                                                                                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OS-MKEK  | AES 128 Master key used to encrypt only the PIN objects stored in flash memory. This key is generated on OS startup using CTR_DRBG, unique for each card.                                                                                                          |

| OSD-KENC | AES 128 (SCP03) Master key used by the Crypto Officer to generate SD-SENC (session keys during secure channel establishment). The key belongs to the Issuer Security Domain keyset.                                                                                |

| OSD-KMAC | AES 128 (SCP03) Master key used by the Crypto Officer to generate SD-SMAC. The key belongs to the Card Issuer Security Domain.                                                                                                                                     |

| OSD-DEK  | AES 128 (SCP03) Master key used by the Crypto Officer. Used to directly unwrap the encrypted key being loaded via the PUT KEY command.                                                                                                                             |

| OSD-SENC | AES 128 (SCP03) Session encryption key used by the Crypto Officer to decrypt secure channel data. The role of this key is to preserve confidentiality and authenticity of transmitted data. The key belongs to the Card Issuer Security Domain.                    |

| OSD-SMAC | AES 128 (SCP03) Session MAC key used by the Crypto Officer to verify inbound secure channel data's integrity. The key belongs to the Card Issuer Domain.                                                                                                           |

| SD-KENC  | AES 128 (SCP03) Master key used by Dev (represented on the card by its respective<br>Application Provider Security Domain) to generate SD-SENC session key.                                                                                                        |

| SD-KMAC  | AES 128 (SCP03) Master key used by Dev (represented on the card by its respective<br>Application Provider Security Domain) to generate SD-SMAC session key.                                                                                                        |

| SD-DEK   | AES 128 (SCP03) Master key used by the Dev. Used to directly unwrap the encrypted key being loaded via the PUT KEY command.                                                                                                                                        |

| SD-SENC  | AES 128 (SCP03) Session Encryption key used by Dev (represented on the card by its respective Application Provider Security Domain) used to decrypt secure channel data. The role of this key is to preserve confidentiality and authenticity of transmitted data. |

| SD-SMAC  | AES 128 (SCP03) Session MAC key used by Dev (represented on the card by its respective Application Provider Security Domain) to verify inbound secure channel data integrity.                                                                                      |

Table 3: Critical Security Parameters - Secret Symmetric Keys

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

#### 3.3.2 Public Keys

| Кеу    | Description / Usage                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OS-DAP | RSA 2048 Global Platform Data Authentication Public Key. The Mandated DAP feature is<br>defined by Global Platform and is used to verify the signature of packages loaded into<br>the Module prior to linking them against built-in Java APIs. It is done under the Dev role.<br>Loaded on card with PUT KEY APDU. This key belongs to the Controlling Authority. |

Table 4: Critical Security Parameters - Public Assymetric Keys

#### 3.3.3 PIN

| OS-GPIN | 7 to 16 character string card global PIN represents the contents of Java object that<br>belongs to a PIN instance. This object is always stored encrypted with OS-MKEK key<br>and is never decrypted during PIN match operations. Instead, the candidate PIN value<br>is encrypted in the same fashion and presented for comparison in encrypted form.<br>The OS-MKEK key is used only if the Global PIN is used by a loaded application. |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Table 5: Critical Security Parameters - Global PIN

#### 3.3.4 Audit events and data

| OS-EXP-<br>COUNTER | The counter that increments each time Java engine handles runtime exception to  |

|--------------------|---------------------------------------------------------------------------------|

|                    | protect against excessive exception throwing by the applet. When a threshold is |

|                    | reached the applet execution stops.                                             |

Table 6: Critical Security Parameters - Counters

#### 3.4 FIPS 140-2 Approved Modes of Operation

The CM operates in only one FIPS 140-2 Approved Mode (standard operating mode) entered implicitly upon successful completion of power-on self-tests, i.e. no special action or command is necessary. Only FIPS-approved crypto algorithms are used when providing services to Crypto Officer or User/Application Developer. No other mode of operation exists when a card containing the CM has been issued to an application developer. The reasons behind this approach were to simplify usage and deployment, application development and streamline the validation phase. The internal code also prevents non-authorized use of cryptographic keys in operations for which they were not intended.

For the CM operating in the FIPS 140-2 approved mode, the CM does not allow loading application feature unless there is a Security Domain with MDAP privilege requiring the mandatory DAP Verification of the loaded application to ensure its authenticity using only FIPS approved crypto algorithms.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

During the chip manufacturing process (design and deployment phases) of the card, the CM is still not in the FIPS 140-2 approved mode. Once the module enters operational phase (after being delivered to the customer) specifically when the card is in the SECURED life cycle state as defined by [GP] it enters the FIPS 140-2 approved mode of operation until the card is terminated (Card Mute).

The M7892 executes its code out of flash and CRC16 program integrity check is performed on code flash contents before entering an operational mode. The contents of various key sets and critical security parameters are stored in available EEPROM data memory with each data structure having a validation field (CRC16) that is checked for consistency before each use and recalculated upon any changes in the contents of this structure. Any applet loaded on this CM must undergo its own FIPS 140-2 validation to maintain FIPS 140-2 certification as a module.

The lifecycles and state transitions follow industry standard implementations specified in Global Platform documentation, version 2.2. The Global Platform specification defines module and application life cycle states and state transitions. Each of the on-module cryptographic algorithms including DRNG, TDES, SHA, AES, RSA and ECC has been individually validated for compliance with FIPS requirements [FIPS140-2 Appendix A, FIPS140-2 Appendix C].

#### 3.4.1 Versions and Mode of Operation

Firmware: Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR)V1.0f Hardware: The hardware is identified by a combination of interface package ID, internal hardware part number and commercial part number.

| Packaging Id                                     | Product and Package Combination          |  |  |

|--------------------------------------------------|------------------------------------------|--|--|

|                                                  | with ISO/IEC 7816-3 Interface Only       |  |  |

| S-MD4. 8-8-1                                     | M7892B11, SLE 78CLFX400VPM               |  |  |

| S-MFC6. 8-8-1                                    | M7892B11, SLE 78CLFX400VPM               |  |  |

| PG-USON10-1                                      | M7892B11, SLE 78CLFX400VPM               |  |  |

|                                                  | with ISO/IEC 14443 Interface Only        |  |  |

| P-MS8-2-1                                        | P-MS8-2-1 M7892B11, SLE 78CLFX400VPM     |  |  |

| <b>P-MC8-2-6</b>                                 | 8-2-6 M7892B11, SLE 78CLFX400VPM         |  |  |

| with ISO/IEC 7816-3 and ISO/IEC 14443 Interfaces |                                          |  |  |

| S-COMB. 6- 6-1 M7892B11, SLE 78CLFX408APM        |                                          |  |  |

| <b>P-M8.4-8-3</b>                                | P-MB. 4-8-3 M7892B11, SLE 78CLFX400VPM   |  |  |

| S-COM 0. 6-6-1                                   | M7892B11, SLE 78CLFX408APM               |  |  |

|                                                  | Table 7: Product and Package Combination |  |  |

Table 7: Product and Package Combination

During the power-on process, the CM performs all necessary self-tests and either enters the approved mode of operation or, if any self-test fails, enters a deadlock state until the next reset or power-on.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

To verify that a module is in the approved mode of operation, an operator authenticated to the Card Manager role sends the GET STATUS command with P1 = 1 and P2 = 0. For example: 80F2010000. The CM responds to the GET STATUS command with the format and information described in Table 8.

| Data Element            | Length<br>(bytes) | Value | Associated Version                                                                                                                                                     |

|-------------------------|-------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Approved mode indicator | 1                 | Var   | 0xAA – module is in approved mode<br>0xFF – module is in deadlock state                                                                                                |

| Security Status Word    | 2                 | Var   | Each bit of this word stands for self-test<br>results (1 – test passed, 0 – test failed).<br>In approved mode Security Status Word<br>is equal to Test Permission Word |

| Test Permission Word    | 2                 | Var   | Each bit of this word allows or disallows<br>relative self-test (1 – test is allowed, 0 –<br>test is disallowed)                                                       |

| Test Parameters         | 4                 | Var   | Each pair of bits contains some<br>parameters for relative self-test (for<br>example length of key for test, etc.)                                                     |

Table 8: Versions and Mode of Operations Indicators

#### 3.4.2 CM Identification

After Card initialization the CM is identified using the command GET DATA. It retrieves the chip and configuration data from the card. The configuration data is retrieved using GET DATA tags 0xDF10 and 0xDF11. The response is coded as TLV object. The offsets given in the tables below refer to the offset inside the value part of the TLV object.

Example for GET DATA ('DF10') command / response pair:

® 80CA DF10 00

¬ DF10 81E0 090000...8340 9000

DF10is the tag81E0codes the value length of 224 in two bytes0900..8340is the value part (224 bytes)9000is the status wordOffset 0 corresponds to the value '09', offset 223 to '40'

All listed items below must have (one of ) the expected value(s).

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

| Offset | Length<br>(bytes) | Description                                | Expected value |

|--------|-------------------|--------------------------------------------|----------------|

| 66     | 2                 | Build information (major / minor version)  | '0x007c'       |

| 69     | 1                 | Security profile - FIPS 140-2 level 3 mode | 'D2'           |

| 88     | 1                 | Dynamic reconfiguration disabled           | 'E1'           |

| 89     | 1                 | Templating disabled                        | 'E1'           |

| 91     | 1                 | Reflashing disabled                        | 'E1'           |

#### Table 9: Tag 'DF10'

| Offset | Length<br>(bytes) | Description                            | Expected value |

|--------|-------------------|----------------------------------------|----------------|

| 32     | 1                 | GP Secure Channel Protocol of ISD      | '02' or '03'   |

| 33     | 1                 | GP SCP implementation option of ISD    |                |

|        |                   | - SCP 03                               | '00' or '10'   |

| 131    | 1                 | ISD supports GP command format         | 'E1'           |

| 132    | 1                 | GP configuration (GP ID or general GP) | 'E1' or 'D2'   |

Table 10: Tag 'DF11'

CHAPTER

## **4** Cryptographic Module Ports and Interfaces

This chapter describes the ports and interfaces (physical and logical), the information passing over the four logical interfaces, data that pass over the physical ports, and the Trusted Channel.

#### 4.1 Communication Interfaces

#### 4.1.1 Logical Interfaces

The Cryptographic Module works as a slave processor in order to process and respond to the reader's commands through a well-defined set of Application Protocol Data Units (APDUs) specified in the [GP] standard and some additional Infineon Proprietary APDUs.

| Logical Interface | Description                                      |

|-------------------|--------------------------------------------------|

| Data input        | The input data field of the APDU command         |

|                   | involves the data input interface of the module. |

|                   | All input parameters must pass through this      |

|                   | interface.                                       |

| Data output       | The output data field of the Response APDU       |

|                   | command involves the data output interface of    |

|                   | the module. All output data must pass through    |

|                   | this interface.                                  |

| Control input     | The APDU command header consisting of the        |

|                   | CLA, INS bytes and control-related command       |

|                   | parameters) involves the control input interface |

| Status output     | The status words SW1 and SW2 of the response     |

|                   | APDU command involve the status output           |

|                   | interface. All error codes and output indicators |

|                   | pass through this interface.                     |

| L                 | Table 11: Logical Interface                      |

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

Moreover, the Cryptographic Module provides services to applets through a set of defined APIs:

- 1. Java Card API: This interface is defined by the specification of the basic functions in the Java Card run-time environment, this interface is used by the Applet Developer for the implementation of an applet that is installed in the TOE. Details can be found in [JCAPI].

- 2. IFX API: This API Packages build an API extensions that facilitate APDU processing and certain interactions with the IC platform

- 3. GlobalPlatform API: These interfaces extend the Java programming language with the org.globalplatform.GPSystem interfaces specified in [GP]. The API provides services to Applications (e.g. Cardholder verification, personalization, or security services). It also provides Card Content management services (e.g. card locking or Application Life Cycle State update) to Applications.

#### 4.1.2 Physical Interfaces

The data-oriented I/O interface to the CM is formed by the I/O pad and by the various RF options. The RF interface (radio frequency power and signal interface) enables contactless communication between a PICC (proximity integration chip card, PICC) and a PCD reader/writer (proximity coupling device, PCD). The PCD must be compliant to ISO 14443 1-4 Type A or B. Power supply is received and data are received or transmitted by an antenna which consists of a coil with a few turns directly connected to the IC. Depending on customer orders, the contactless interface options are set by means of blocking either at Infineon premises or at the premises of the user.

The CM communicates with the Card Acceptance Device or card reader (CAD) through a contact-based interface (Figure 5) or a contactless-based interface. The CAD must be compliant with the ISO 7816 1-3 standard. At no time are private and secret keys, authentication data, or CSPs imported or exported in plaintext. The dedicated path is available by means of a GlobalPlatform Secure Channel.

At start-up, an ISO 7816 interface is established as the communication channel with the host for the duration of the session. During a session, all logical paths are carried on the chosen physical path. The interface with the host computer is a command-response interface, where all communication with the host is inhibited until a command is executed. In particular, a command to generate a key or key pair causes communication with the host to be suspended until the key generation is either completed successfully or aborted. At the conclusion of most operations, a response message is returned to the host containing only the return status code.

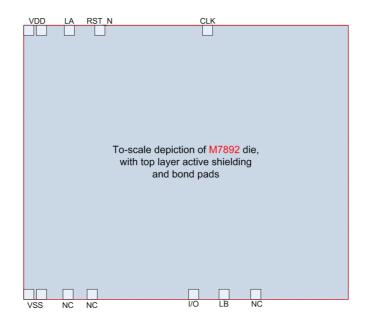

The CM has 8 ISO 7816 compliant electrical contacts referred to as C1 through C8 in Figure 5 and described in Table 12 below. However, C4, C6, and C8 are not electrically connected to the embedded IC pads shown in Figure 6 and are unused. Table 13 describes the IC pads and their logical interface type.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

Figure 5: ISO 7816 Interface Contact Pad Designations and Locations

| Contact | Designation | Use                                                                                                                                                                                                                        |  |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C1      | Vcc         | Power connection through which operating power is supplied to the microprocessor chip in the card                                                                                                                          |  |

| C2      | RST         | Reset line through which the IFD can signal to the smart card's microprocessor chip to initiate its reset sequence of instructions                                                                                         |  |

| С3      | CLK         | Clock signal line through which a clock signal can be provided to the microprocessor<br>chip. This line controls the operation speed and provides a common framework for<br>data communication between the IFD and the ICC |  |

| C4      | NC          | Not used.                                                                                                                                                                                                                  |  |

| C5      | GND         | Ground line providing common electrical ground between the IFD and the ICC                                                                                                                                                 |  |

| С6      | NC          | Not used. Programming power connection only used to program EEPROM of first generation ICCs.                                                                                                                               |  |

| С7      | 1/0         | Input/output line that provides a half-duplex communication channel between the reader and the smart card                                                                                                                  |  |

| C8      | NC          | Not used.                                                                                                                                                                                                                  |  |

Table 12: CM ISO 7816 Interface Contact Assignments

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

Figure 6: IC Die Pad Designations and Locations

| Pad      | Description                | Logical Interface Type                           |

|----------|----------------------------|--------------------------------------------------|

| VSS, VDD | ISO 7816: Power and ground | Power                                            |

| CLK      | ISO 7816: Clock            | Control in                                       |

| RST_N    | ISO 7816: Reset            | Control in                                       |

| 10       | ISO 7816: Serial interface | Data in, data out, control in, status out        |

| LA, LB   | ISO 14443: Antenna         | Data in, data out, control in, status out, power |

| NC       | No connect                 | Not used                                         |

The minimum contact surface area is 1.7mm \* 2.0 mm. Contact dimensions for C1 through C8 are:

- Length 85.5mm

- Width 54.0mm

- Thickness 0.80mm

Table 14 describes the connections between the logical interfaces and the physical interfaces.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

| Logical Interface | Physical Interface     |

|-------------------|------------------------|

| Data input        | Command Interface (C7) |

| Data output       | Command Interface (C7) |

| Control input     | Command Interface (C7) |

| Status output     | Command Interface (C7) |

Table 14: Logical Interfaces With Physical Interface Connections

#### 4.2 Packages

All product derivatives are identical from module design, layout and footprint, but are different in their possibilities to connect to different types of antennas or in their ability to be implemented in special packages for different form factors.

The CM covers 3 types of package families:

- 1. with ISO/IEC 7816-3 Interface Only

- 2. with ISO/IEC 14443 Interface Only

- 3. with ISO/IEC 7816-3 and ISO/IEC 14443

The following table contains the CM and Package combination Identifications:<sup>4</sup>

| Packaging Id  | Product and Package<br>Combination | Front Image    | Back Image |

|---------------|------------------------------------|----------------|------------|

|               | with ISO/IEC 7816-3                | Interface Only |            |

| S-MD4. 8-8-1  | M7892B11, SLE 78CLFX400VPM         |                |            |

| S-MFC6, 8-8-1 | M7892B11, SLE 78CLFX400VPM         |                |            |

| PG-USON10-1   | M7892B11, SLE 78CLFX400VPM         | •              | •          |

<sup>4</sup> The smallest squares of the background are 1mm x 1mm

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

| Packaging Id          | Product and Package<br>Combination | Front Image            | Back Image |  |  |

|-----------------------|------------------------------------|------------------------|------------|--|--|

|                       | with ISO/IEC 14443 Interface Only  |                        |            |  |  |

| P-MS8-2-1             | M7892B11, SLE 78CLFX400VPM         |                        |            |  |  |

| P-MC8-2-6             | M7892B11, SLE 78CLFX400VPM         |                        |            |  |  |

| 0.0000.0.0.1          | with ISO/IEC 7816-3 and IS         | U/IEC 14443 Interfaces |            |  |  |

| S-COM <b>S.</b> 6-6-1 | M7892B11, SLE 78CLFX408APM         |                        |            |  |  |

| <b>P-M8.4-8-3</b>     | M7892B11, SLE 78CLFX400VPM         |                        |            |  |  |

| S-CQM 0. 6-6-1        | M7892B11, SLE 78CLFX408APM         |                        |            |  |  |

Table 15: Supported Packages

CHAPTER

# **5** Roles, Services and Authentication

This chapter describes the roles, services, and authentication provided by the CM.

#### 5.1 Roles

The CM supports identity-based authentication. There are two roles that operators may assume: a Crypto Officer role and Developer role (see Table 16 below). The CM does not support concurrent operators and clears previous authentications on power cycle.

| Role                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Authentication                                                                                                                                                                                       |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                           | Cryptographic Officer Role                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |  |  |  |

| Card<br>Manager/Crypto<br>Officer<br>(CO) | This role is responsible for card issuance<br>and executable content management,<br>security domains configuration and card<br>content management via the Card<br>Manager / Issuer Security Domain. The<br>Crypto Officer authenticates to the<br>module through the GlobalPlatform<br>mutual authentication protocol based on<br>symmetric cryptography (SCP-03). Once<br>Crypto Officer is authenticated it is<br>possible to execute the services provided<br>by the (ISD).<br><u>This role can only be active when the ISD is<br/>currently selected.</u> | Identity type authentication by<br>demonstrating the knowledge of<br>secret AES keys such as OSD-KENC<br>and OSD-KMAC during the first<br>phase of Secure Channel (SCP03)<br>Establishment with ISD. |  |  |  |

|                                           | User Role                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |  |  |  |

| Applet Developer<br>(Dev)                 | Considered an internal, privileged user of<br>the platform. Entities in this role create<br>and deploy smart card applets that utilize<br>JavaCard APIs as the only means of                                                                                                                                                                                                                                                                                                                                                                                  | Identity type authentication based<br>on SD-KENC and SD-KMAC during<br>the first phase of Secure Channel<br>(SCP03) Establishment with                                                               |  |  |  |

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

| communicating with OS internals. The        | Application Provider's Security    |

|---------------------------------------------|------------------------------------|

| Applet Developer is in charge of installing | Domain. The Applet Developer       |

| and managing their own applications in      | must demonstrate the knowledge of  |

| their respective Application Provider       | secret AES keys that belong to the |

| Security Domain (APSD) on the card. The     | Application Security Domain        |

| Applet Developer must be authenticated      | associated with that Applet        |

| to their respective Security Domain         | Developer.                         |

| through GP's mutual authentication          |                                    |

| protocol based on SCP-03. They are          |                                    |

| represented on the card by their            |                                    |

| respective APSD.                            |                                    |

| This role can only be active when the APSD  |                                    |

| is currently selected.                      |                                    |

Table 16: Roles

#### 5.2 Services

Services provided by the CM can be divided in two groups.

Services in the first group are available to off card entities. Such services are related to card content management (e.g. applet loading, installation, deletion, card data access or storage) accessed via communication protocols like ISO7816.

The second group of services is services available to on card entities, i.e. Java Card applets. These services are typically cryptographic services available via the Java Card API.

#### 5.2.1 Card Management Services Available to off Card Entities

Card content management services can be further subdivided into two groups.

1) Services that do not handle CSPs and do not require authentication. For instance, applet selection or requesting publicly accessible data stored on the card. These services are accessible in CO, and DEV roles without a need for authentication.

2) The services in this group allow for modification or access of CSPs and perform card content management operations. For instance, applet installation and deletion, keyset placement and package loading/deletion. These services are critical to the overall security of the card and are accessible only to the CO and DEV roles usually by authenticating with a corresponding Security Domain.

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3 This document may be freely reproduced and distributed whole and intact, including this copyright notice.

#### 5.2.1.1 Non Authenticated Services

| Service                   | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CARD RESET<br>(Self-test) | Power cycle the Module by removing and reinserting it into the contact reader<br>slot, or by reader assertion of the RST signal. The Card Reset service will invoke<br>the power on self-test sequence described in Section, and<br>On any card reset, the card deletes the number of security exceptions thrown and<br>clears its velocity checking counters. |

| INITIALIZE UPDATE         | Initialize the Secure Channel; to be followed by EXTERNAL AUTHENTICATE when<br>the session keys are generated.<br>Does not use CSPs.                                                                                                                                                                                                                           |

| GET DATA                  | Retrieve one public data object. Does not use CSPs. GET DATA honors GP access control rules; see below for the variation of GET DATA for objects that require authentication.                                                                                                                                                                                  |

| SELECT                    | Select an applet, returning application template. Does not use CSPs.                                                                                                                                                                                                                                                                                           |

| MANAGE<br>CHANNEL         | An APDU command used over I/O interface to open or close a logical channel on that same interface.                                                                                                                                                                                                                                                             |

Table 17: Unauthenticated Services

#### 5.2.1.2 Services Requiring Authentication and Manipulating CSPs

Note that the only difference between the services provided to CO and those to Dev is the Security domain that they are interacting with. For instance, by sending an "EXTERNAL AUTHENTICATE" command, the CO can open an SCP session only with the ISD whereas the Dev will be only communicating with the APSD.

| Service    | Description                                                                                                                                                           | Keys and CSP's                                                          | CO | Dev | Level of<br>Access |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----|-----|--------------------|

| DELETE     | Delete an applet, security domain or<br>keyset from EEPROM. On any card reset,<br>the card deletes the number of security<br>exceptions and clears velocity counters. | OSD-SENC, OSD-<br>SMAC (AES keys for<br>GP secure channel<br>operation) | X  | Х   | w,e                |

| GET STATUS | Retrieve information about the card.<br>Does not use CSPs.                                                                                                            | None                                                                    | Х  | Х   | r,e                |

| INSTALL    | Informs the Card Manager that Card<br>Content management steps are being<br>processed. Uses the (GP secure channel<br>operation).                                     | OSD-SENC, OSD-<br>SMAC (AES keys for<br>GP secure channel<br>operation) | X  | Х   | r,w,e              |

Security Policy for Java Card Platform Implementation for Infineon on SLE 78 (SLJ 52GxxyyyzR) V1.0f Version 2.3

This document may be freely reproduced and distributed whole and intact, including this copyright notice.

| Service                  | Description                                                                                                                                                                   | Keys and CSP's                                                                                                                                                                                                 | CO | Dev | Level of<br>Access |